文章目录

一.原理图输入实现全加器

1.新建工程

点击File->New Project Wizard…

选择开发板

选择仿真软件

2.新建半加器原理图文件

点击File->New->Block Diagram/Schematic File

在工具栏选择相应元件,组成如下线路

将该文件保存为half_adder.bdf,并点击如下图标进行编译

若产生报错,则线路存在问题,如某些地方线路没连上,如果仅仅是警告信息,则可忽略。

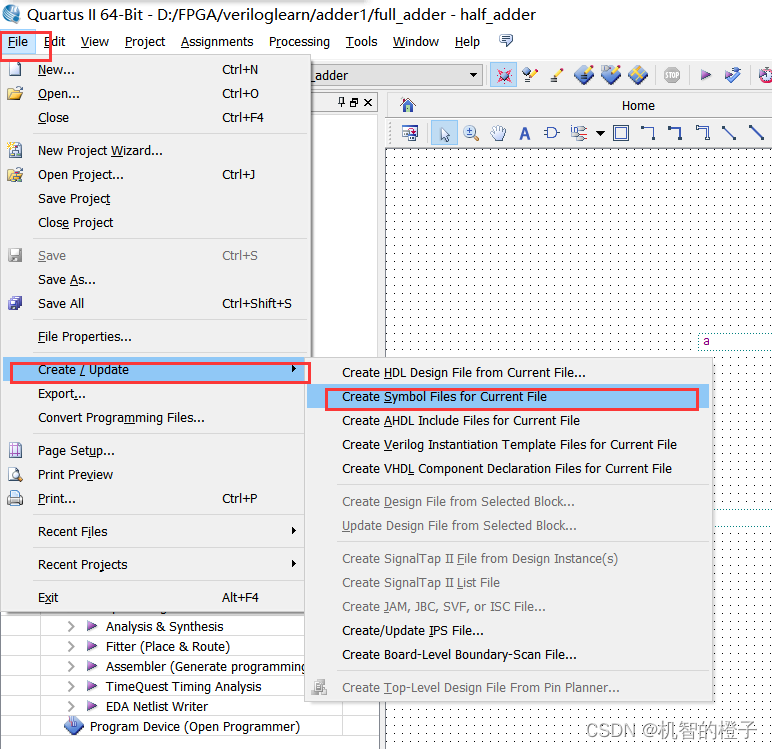

将项目设置成可以调用的元件

点击File->Create/Update->Create Symbol Files for Current File

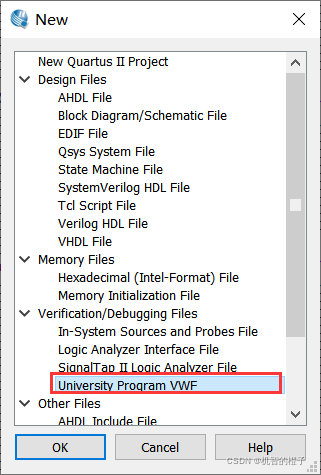

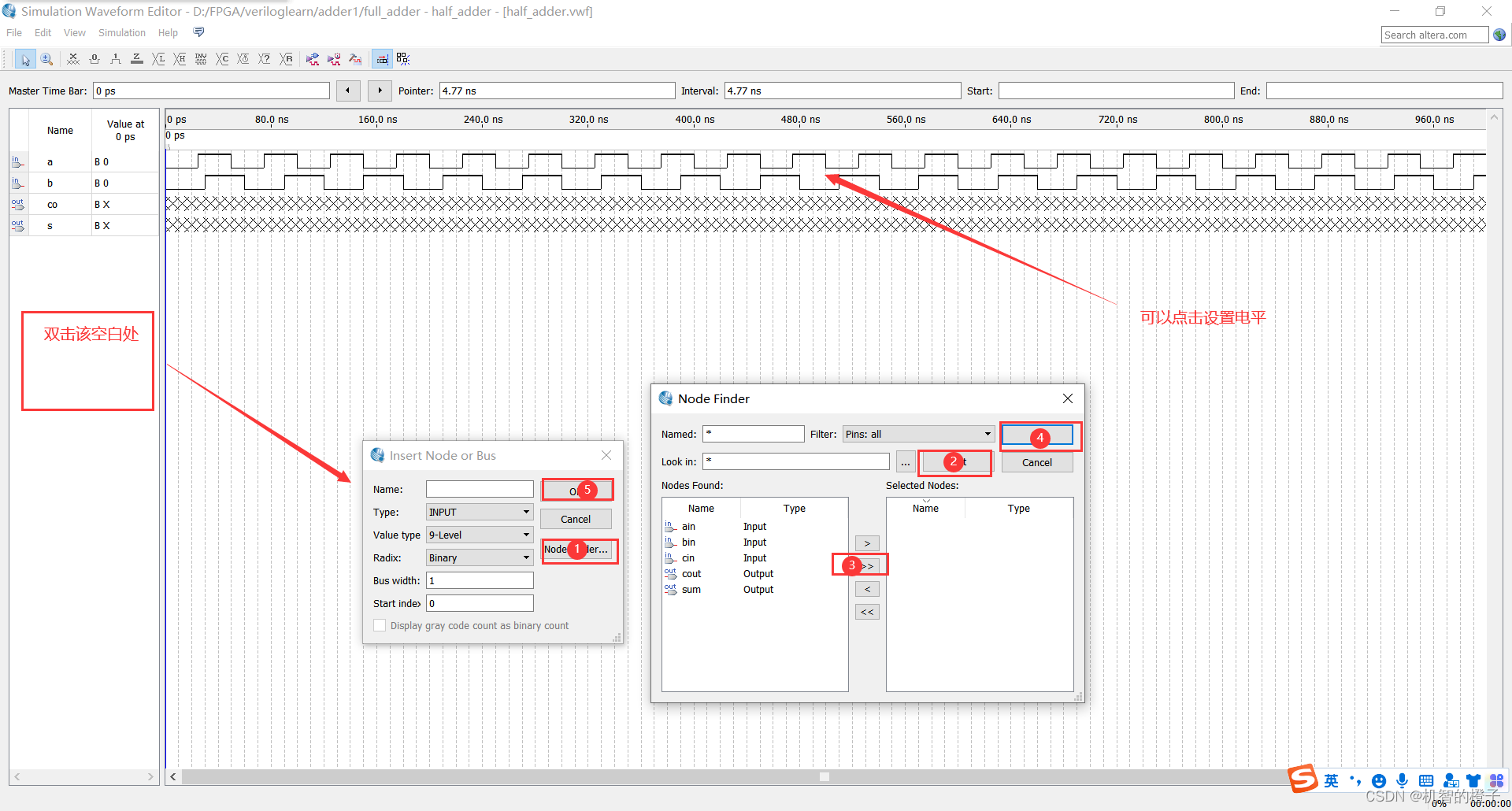

3.新建半加器波形文件

将文件保存为half_adder.vwf 【注意!!!这里的文件名要和前面对应原理图的文件名一致,否则不能仿真】

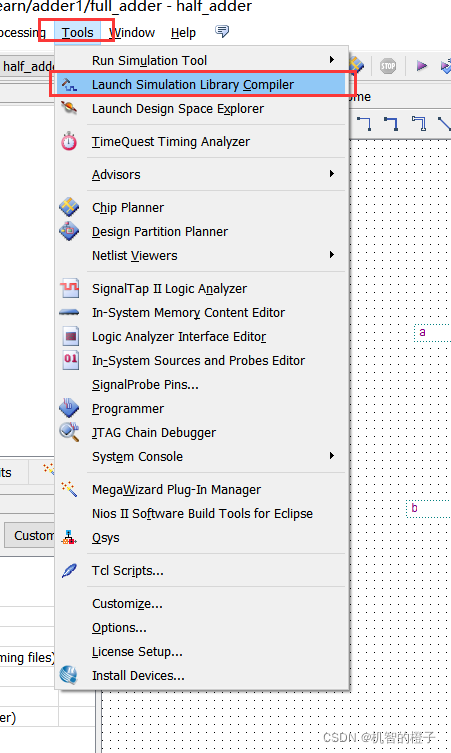

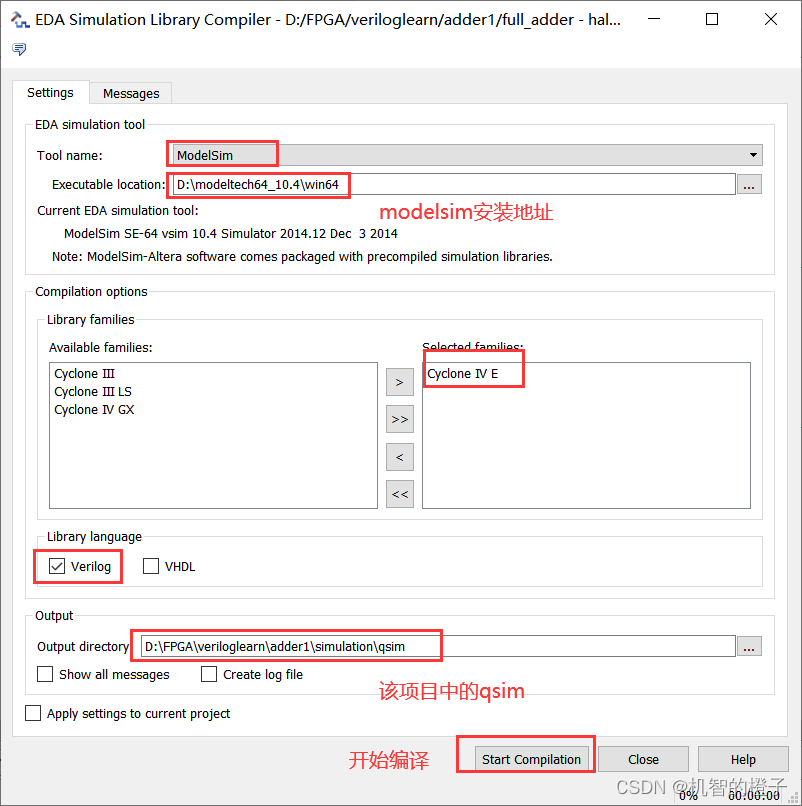

仿真前编译一下

点击Tools->Launch Simulation Library Compiler

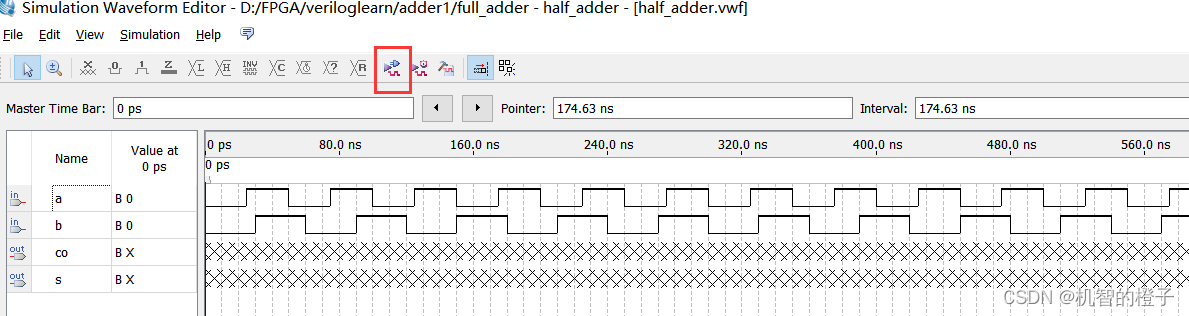

编译没有错误,回到波形图,点击如下按钮,开始仿真

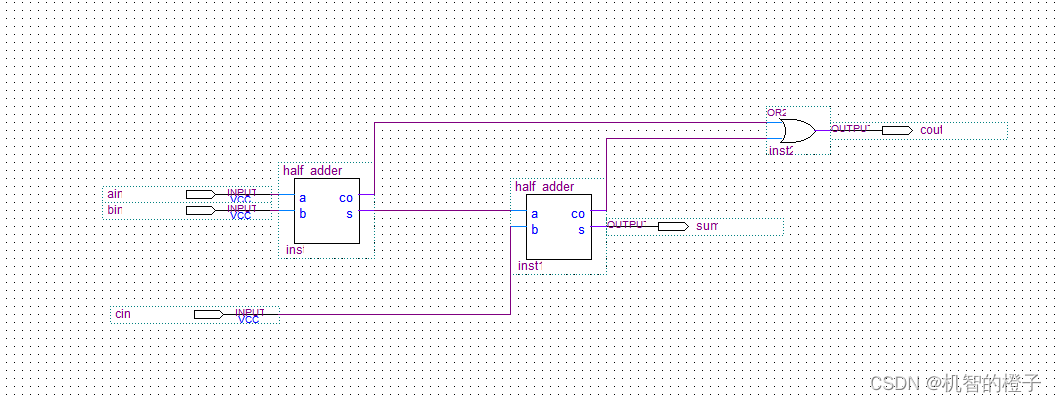

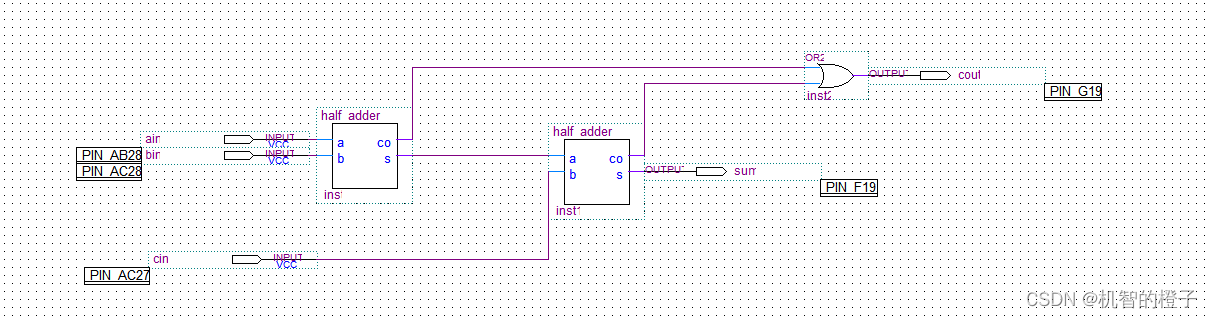

4.新建全加器原理图文件

新建文件同上,命名为full_adder.bdf

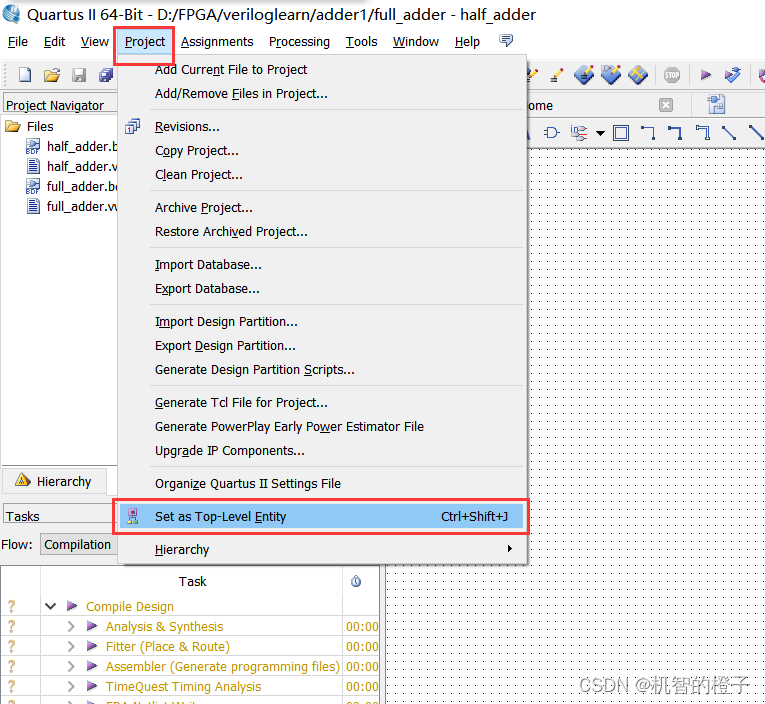

这里用到了上面的半加器元件,同时将该实体设为顶层文件

5.新建全加器波形文件

同上新建,同时命名为full_adder.vwf

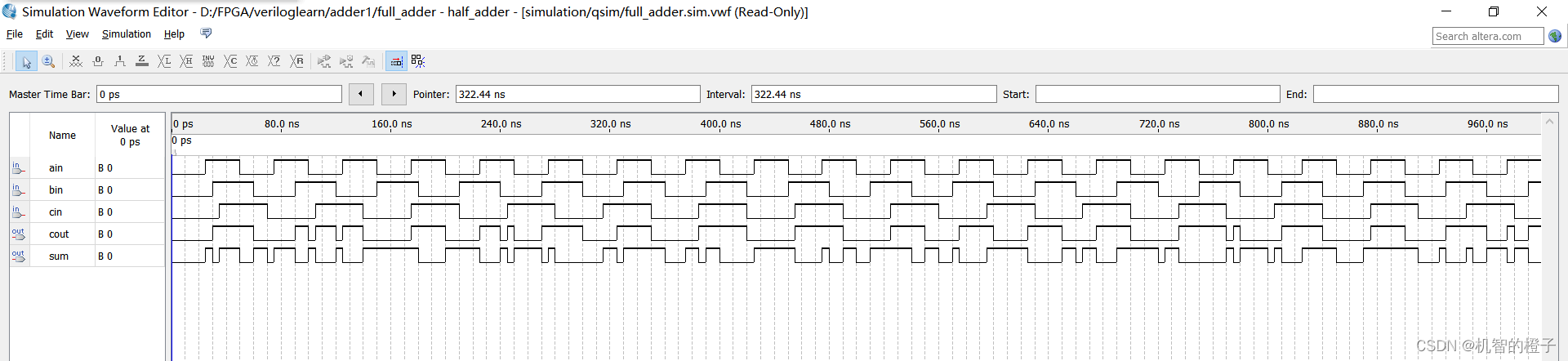

编译仿真,结果如下:

6.硬件绑定及下载测试

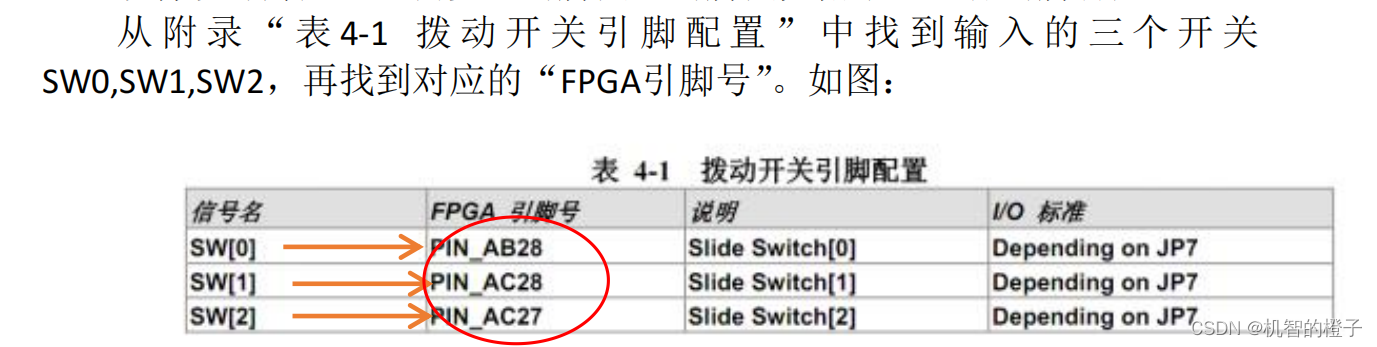

查看开发板引脚图,找到相关引脚,将需要使用的引脚,绑定到原理图上对应的输入处

相应找到LED引脚配置为输出

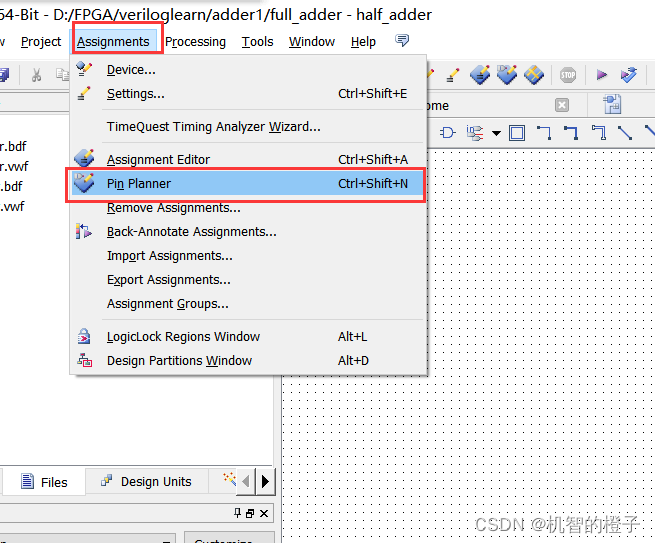

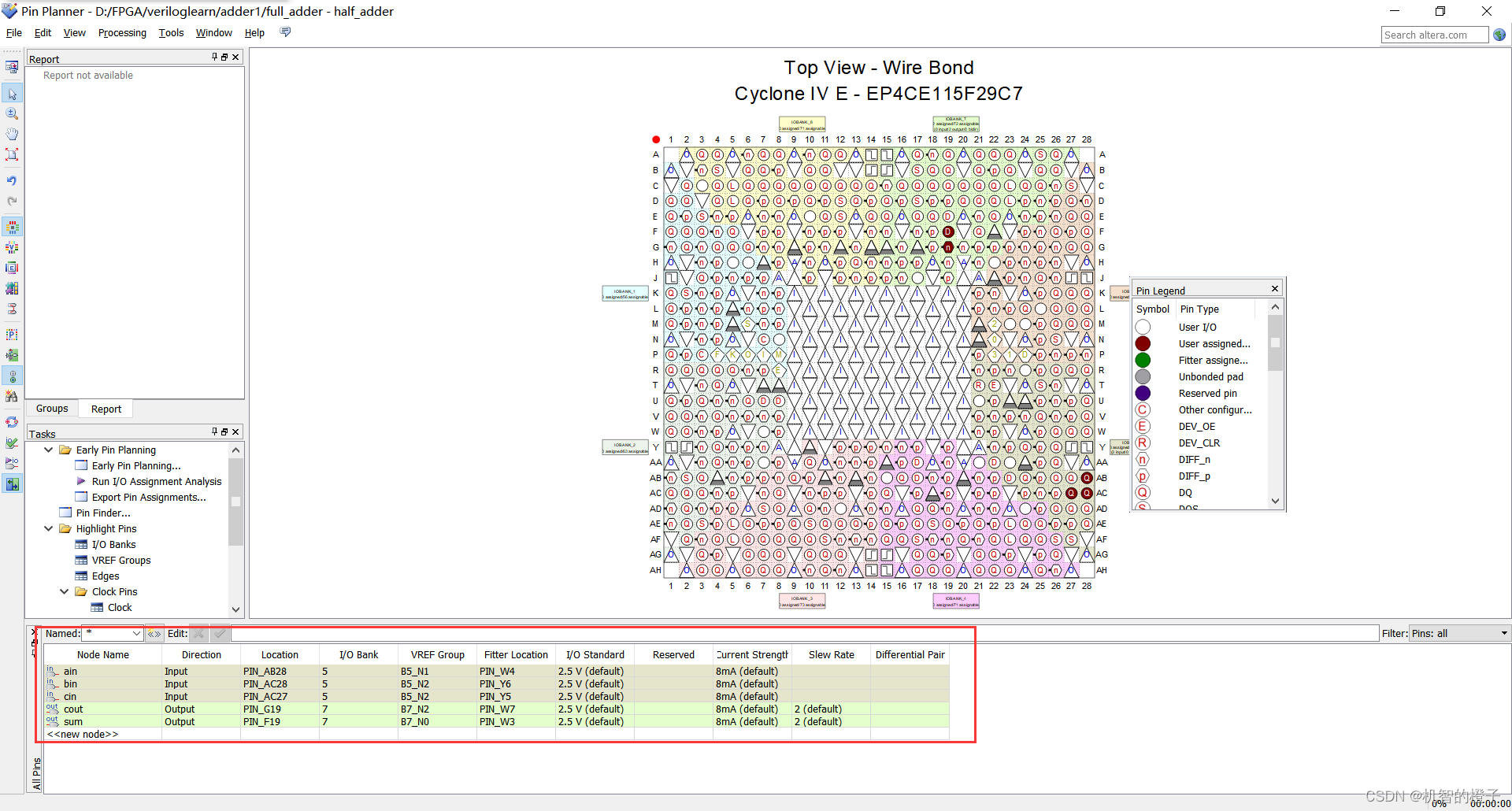

绑定引脚

绑定成功

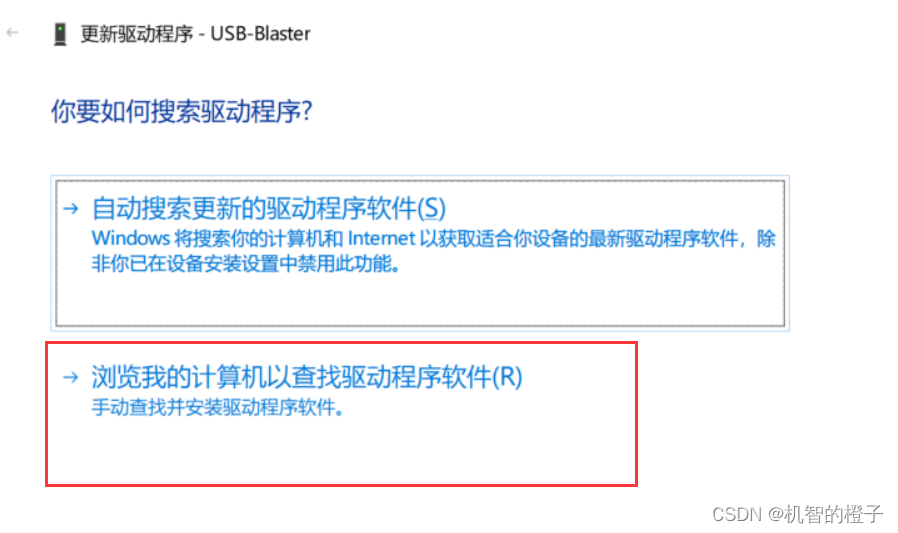

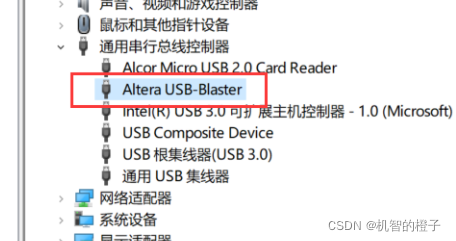

将连接线的USB端连接到电脑,另一端连接到开发板的USB_blaster端口,打开设备管理器,找到其他设备

右键点击,选择更新驱动程序软件

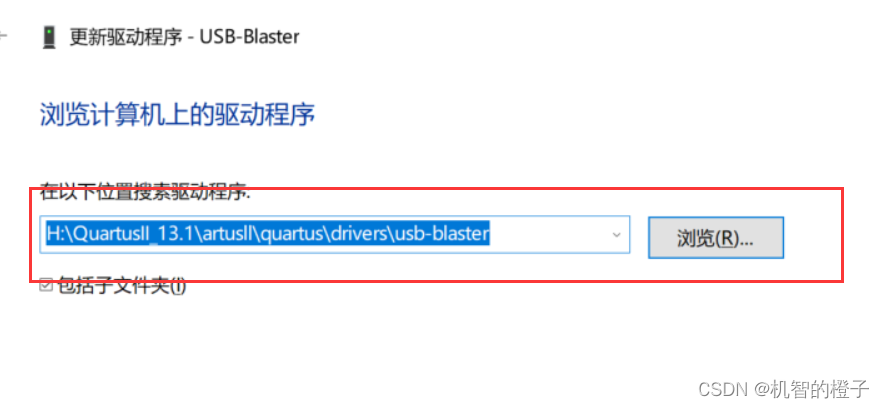

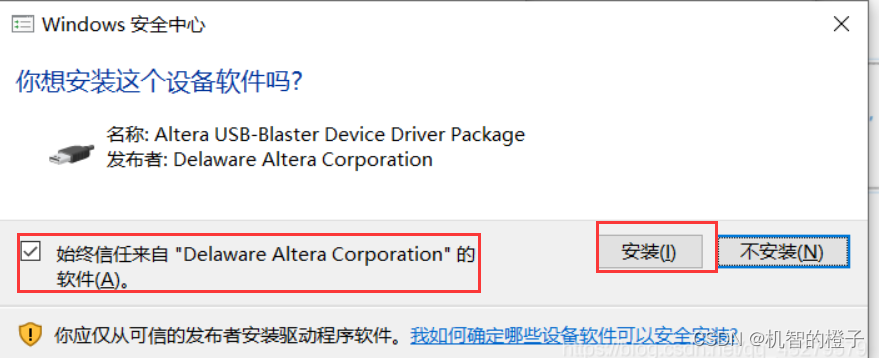

在自己安装Quartus的文件下找到该文件

安装成功,能够在该处看见

下载测试

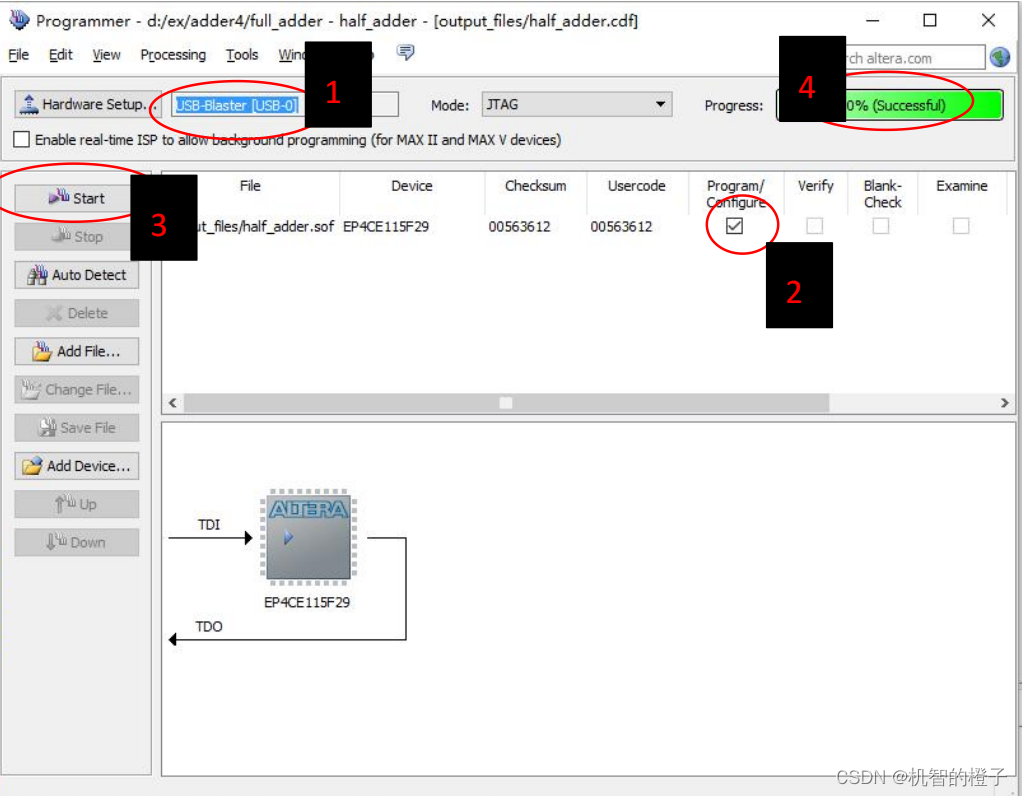

把开发板接上电源,USB 接口接电脑。打开电源开关(注意不用下载时请一定关闭开关,以免烧坏板子)。点击软件工具栏上的按钮 ,则出现下载界面。第一次下载需安装硬件。即在下载界面中点击按钮“hardware setup…”,然后在弹出的对话框中选择“USBblaster”,再点击“ok”,则硬件被安装上。

安装好硬件后,在下载的.sof文件后打钩,再点击start,看到100%(successful),下载成功

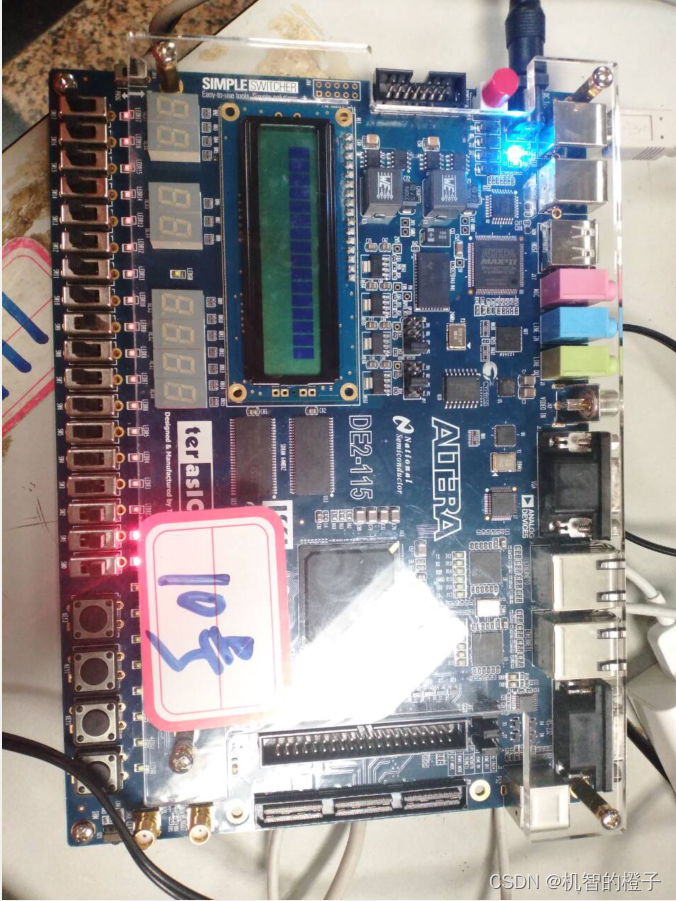

观察到硬件

二.Verilog语言实现全加器

1.新建工程

同上

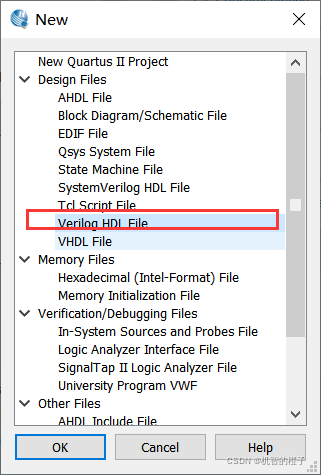

2.新建Verilog文件

添加以下内容

module fuladder(a,b,ci,s,co);//考虑进位的加法器模块

// 请在下面添加代码,完成一位全加器功能

/* Begin */

input a,b;

input ci;

output s;

output co;

assign {co,s}=a+b+ci;

/* End */

endmodule

保存文件为fuladder.v

编译不报错。

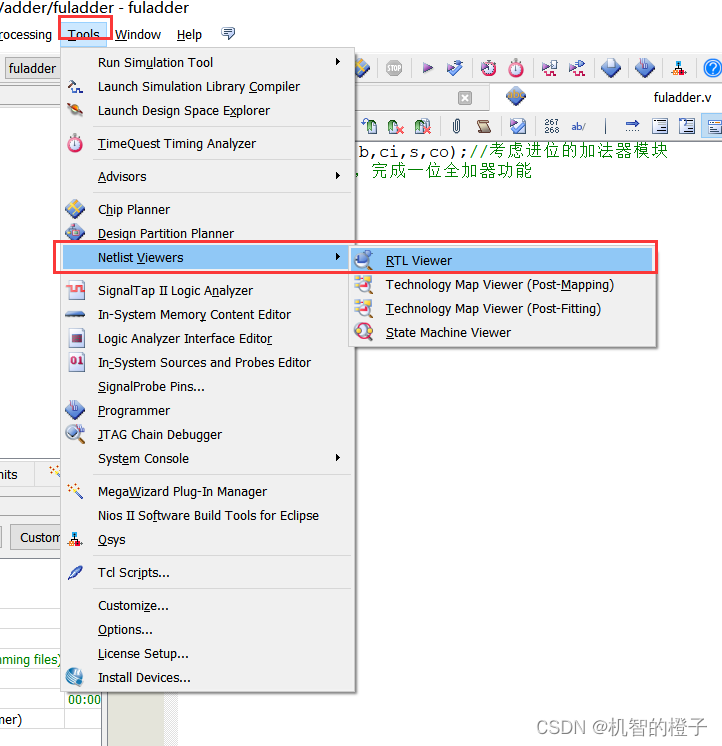

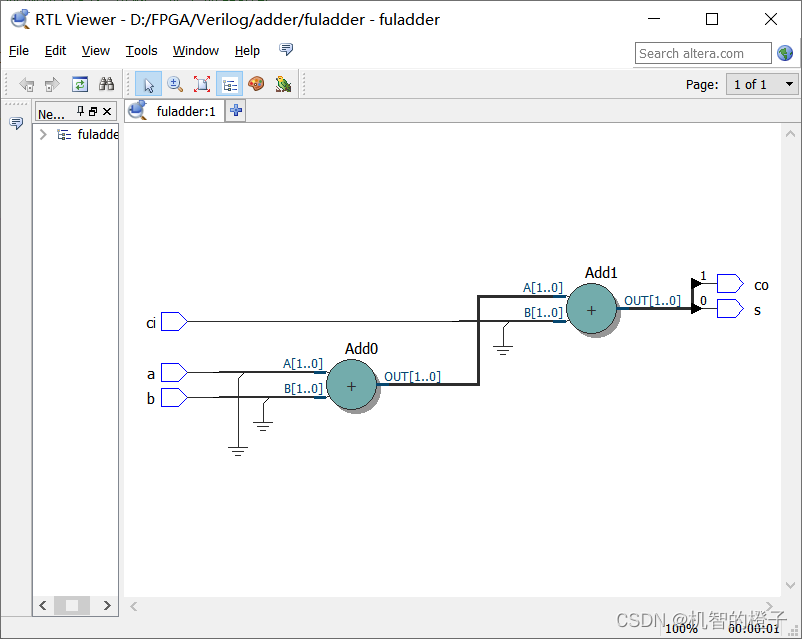

使用rtl viewer查看硬件电路图

硬件电路图

3.新建波形文件

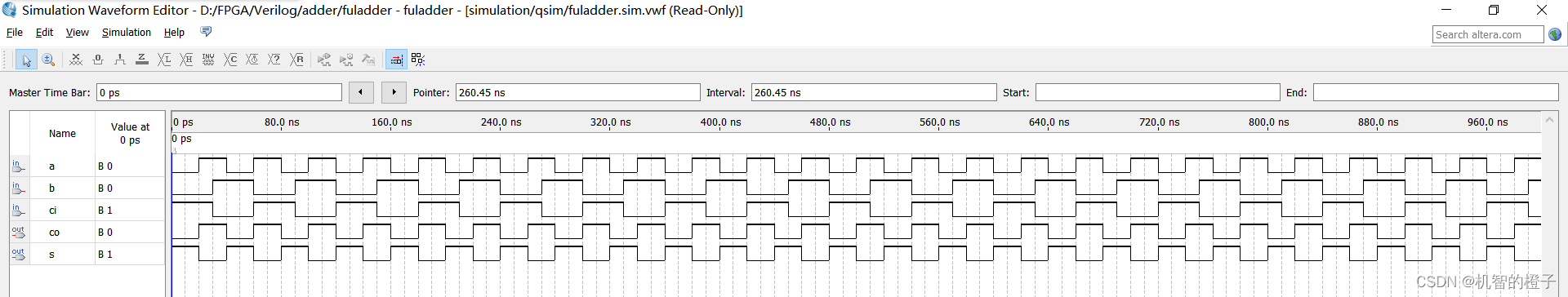

波形文件保存为fuladder.vwf,并编译仿真,结果如下:

三.总结

利用Quartus和modelsim软件能够简化FPGA电路设计以及测试,特别是Verilog语言能够帮助完成底层设计,设计时,我们只关注输入输出之间的关系就可以了。

四.参考链接

https://blog.csdn.net/qq_43279579/article/details/115158140

https://blog.csdn.net/qq_43279579/article/details/115176423