内存概念整理

引言

本文主要记录哪些问题?

1. DDR 是个什么东西,然后如何演变的;

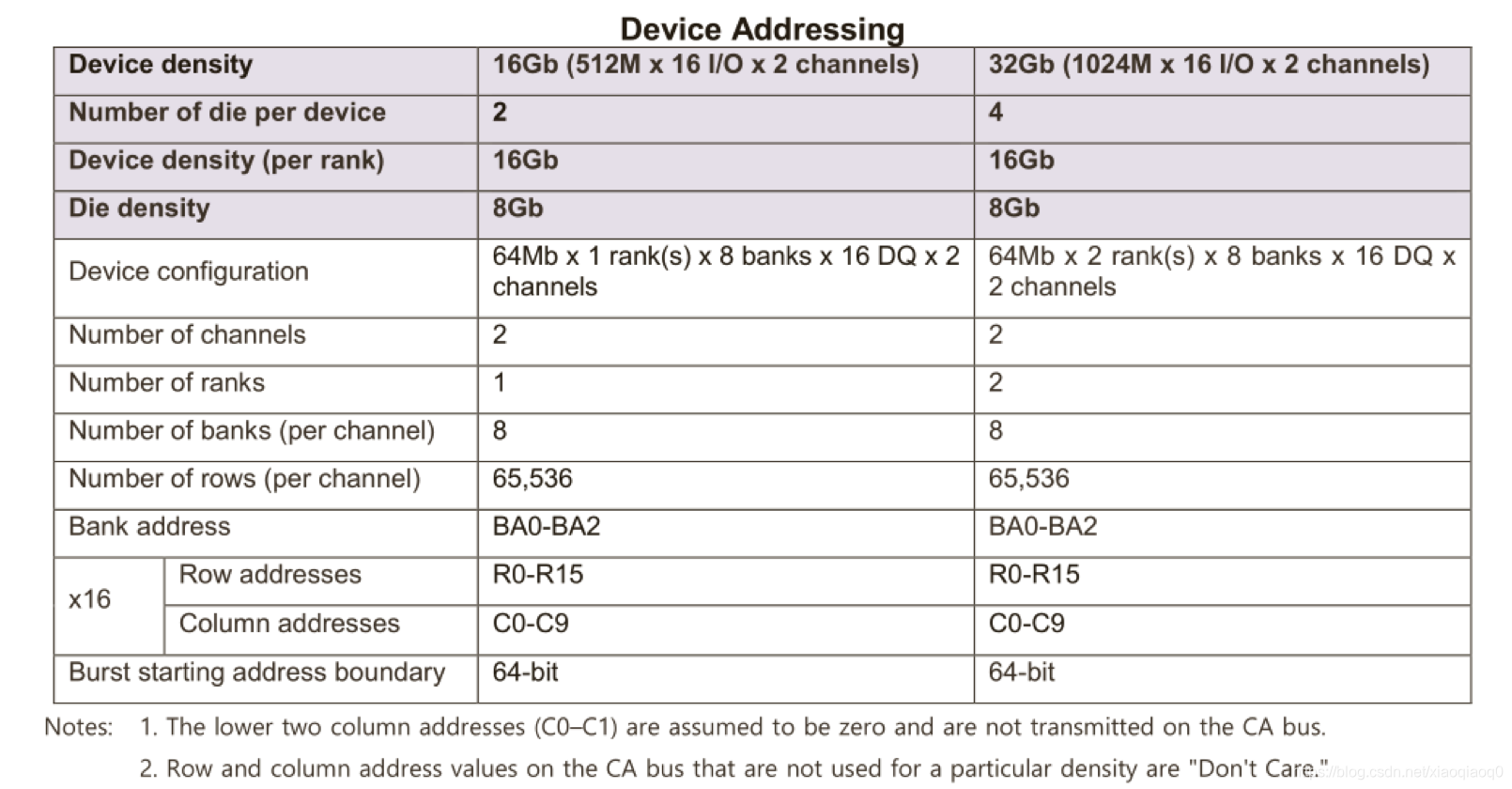

2. DDR 中容量怎么计算,涉及到的bank、rank、channel、die分别是为了解决什么问题的?

3. DDR 与SOC 地址线如何连接,DDR寻址过程具体是怎样的?

1. 物理内存

1.1 内存概念

所谓内存,是指计算机在运行时,需要使用的数据的存放介质;

– 数据读写速度快;

– 断电数据消失,通过一定频率的电流刷新维持内部状态,断电后状态会恢复初始,即数据消失;

– 价格相对于nand、emmc等闪存比较贵;

根据上述特性,在计算机系统中,该部分被用做运行内存,即上电后将数据从存储介质中拷贝到运行内存,提供给到CPU使用;

最小系统:CPU、DDR、EMMC为计算机的三个核心部件,即计算机要运行起来,必须依赖上述核心部件;

1.2 DDR 发展过程

Random-Access Memory,随机存储器,主要分为:

- static Random-Access Memory:不需要一直刷新,只要通电即可保证数据存在;

- dynamic Random-Access Memory:需要周期性的更新,才可保证数据一直存在;

显然,静态比动态会更贵一些(体积大,功耗大),所以一般只是内置在SOC中作为cache使用;

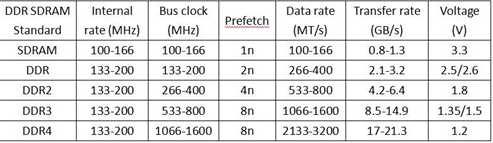

目前常见的运行内存都是基于SDRAM技术基础上提升而来,简单罗列:

| name | 存储器工作clk | IO总线clk | 数据速率 | 预取数据 | 电压 |

|---|---|---|---|---|---|

| SDR SDRAM | 100 | 100 | 100 | 1bit | NA |

| DDR SDRAM | 100 | 100 | 200 | 2bit | NA |

| DDR2 | 100 | 200 | 400 | 4bit | 1.8V |

| DDR3 | 100 | 400 | 800 | 8bit | 1.5V |

| DDR3L | 100 | 400 | 800 | 8bit | 1.35V |

| LPDDR3 | 100 | 400 | 800 | 8bit | 1.2V |

| DDR4 | 100 | 800 | 1600 | 8bit | 1.5V |

| LPDDR4 | 100 | 800 | 1600 | 8bit | 1.2V |

速率提升主要体现在如下两个方面:

- clk上升沿和下降沿都取数据,数据传输是工作频率的2倍;

- IO总线上一次预取2、4、8bits的数据,则IO总线频率是记忆存储芯片工作频率的N倍;

PS: 上述频率只是说明比例关系,而非仅支持该频率

大体是这么个逻辑:

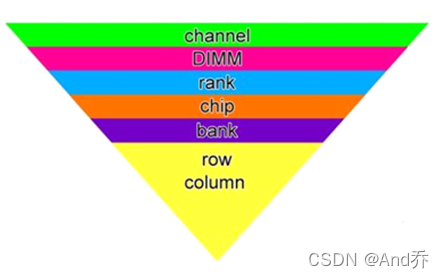

1.3 DDR 内部逻辑结构组成

| 单位描述 | 描述 | 容量(bit) | |

|---|---|---|---|

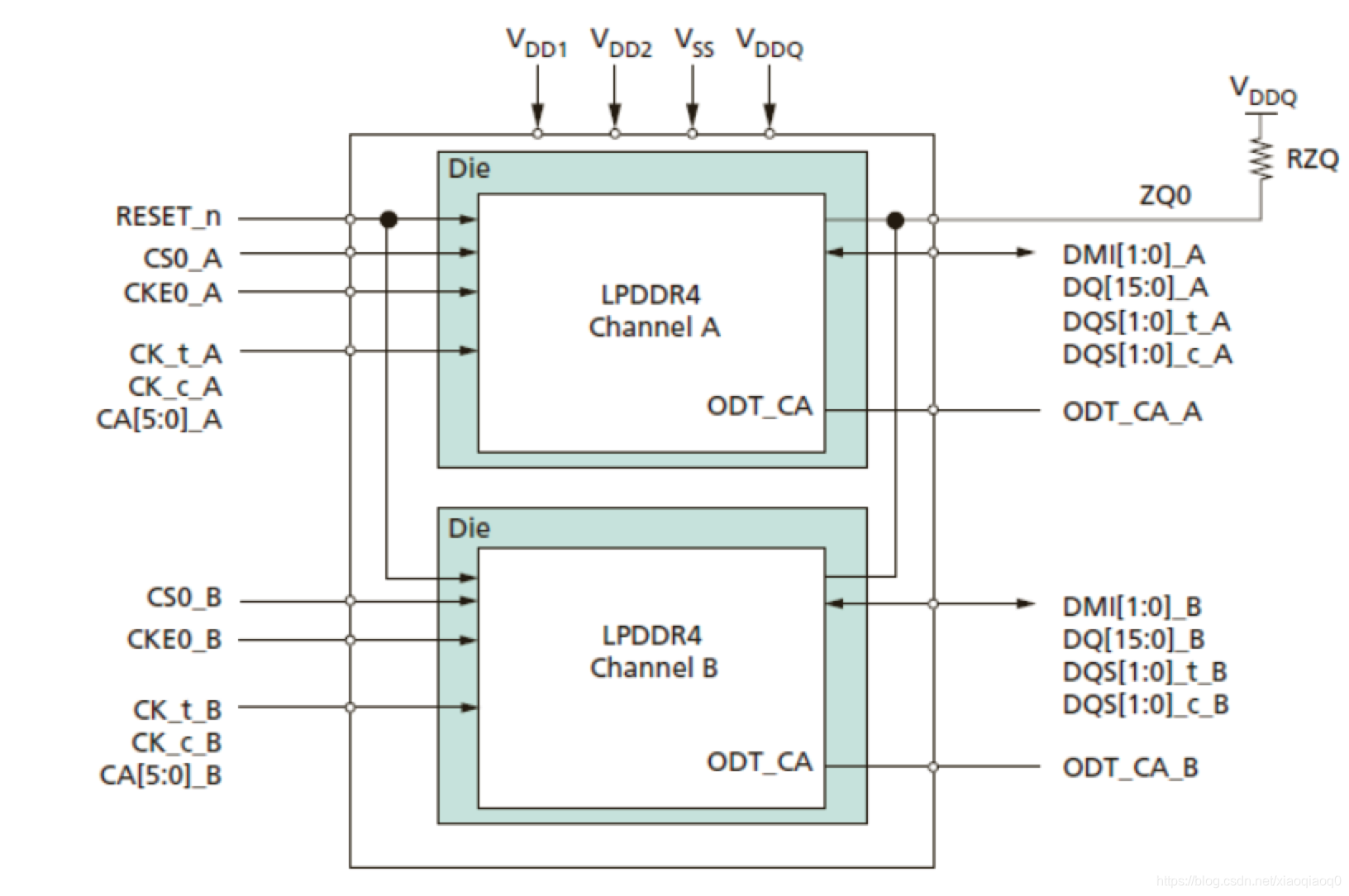

| Channel | 使用相同的行列地址,并联操作 | 根据容量有1~2个Die,目前接触到的 | 用于数据线匹配,可以支持两个ch各自16bit组成32bit |

| rank | 满足SOC连接的数据线叫做一个rank,一个device 内部有更多bits可供选择,则叫做2 rank | row * col * bank * IO | 用于扩容 |

| DDR Device | 实际贴片的产品 | row * col * bank * IO * ch * rank | 实际肉眼可见的IC |

| 存储阵列 | 一个行列阵,包含r行c列个存储单元 | row * col | 通过行列可以确定唯一存储单元,根据spec不同而有X8、X16 |

| 存储单元 | 最小存储单元 | X8、X16 | 与一个地址对应 |

| 预取位宽 | DDR3/4技术支持一次取8bitt | row * col * bank | 这个理解为1.2小节中最后一张图 |

| 晶圆(Die) | 封装容器 | row * col * bank * IO,LPDDR4 大多为8Gbit | 需要使用CS选择使能 |

对应如下图示:

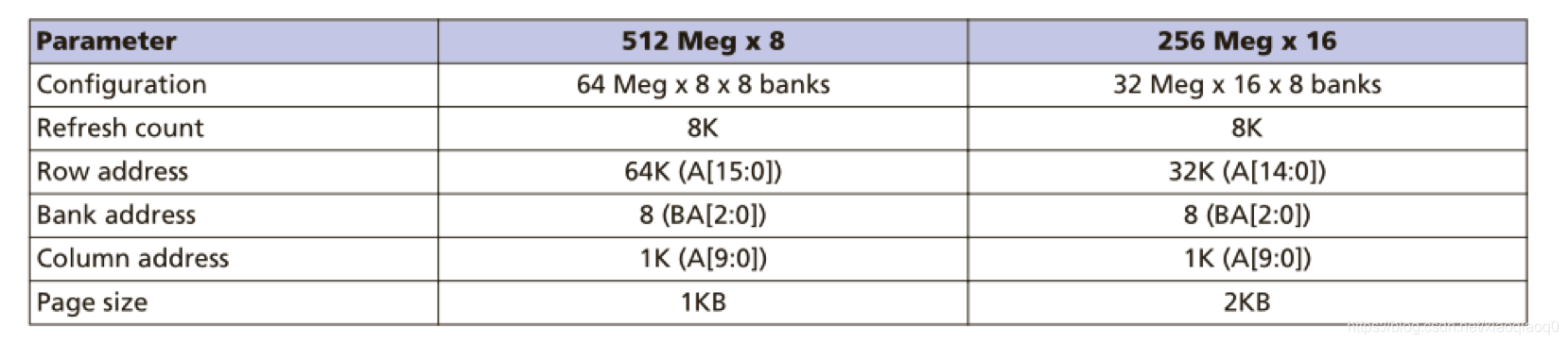

1.4 地址线的计算

要理解上述概念,还需要实际确认两个概念:

- 容量如何组成;

- 如何寻址;

地址线的组成,按照4GB 容量、32根DQ线、DDR4标准来看:

- 4GB = 32Gbit , 一次取32bits数据,由于DDR4一次可以预取16bit数据,需要2个channel或者2颗DDR device,则划分为2^30个地址,理论需要30根地址线;

- 由于行列地址线复用,则可以提供 行 * 列 * bank相当于29根地址线,实际有16 + 3 = 19根地址线 ,提供512Mbit 容量,则还差一位;

- 最后一根地址线由CS信号充当这个角色;

容量:

- 32bits DQ,对于DDR3则需要4个(可能存在4个单channel或者2个双channel),对于DDR4则需要2个(可能存在2个单channel、或者1个双channel)

- 则地址分了组,一组32bits,4Bytes,所以还需要 容量/4 再取一个log2,这些就划分在row 、 col、 bank 、CS(rank、cahnnel、die都体现在这里);

我们常说的8bit、16bit是指的一颗DDR的数据线(DQ),则一般和32bits(目前接触到的都是32bits)的SOC组合的话,需要4片8bit或者2片16bit或者1片32bit,即对于SOC来讲,他认为自己读取到的就是1片DRAM

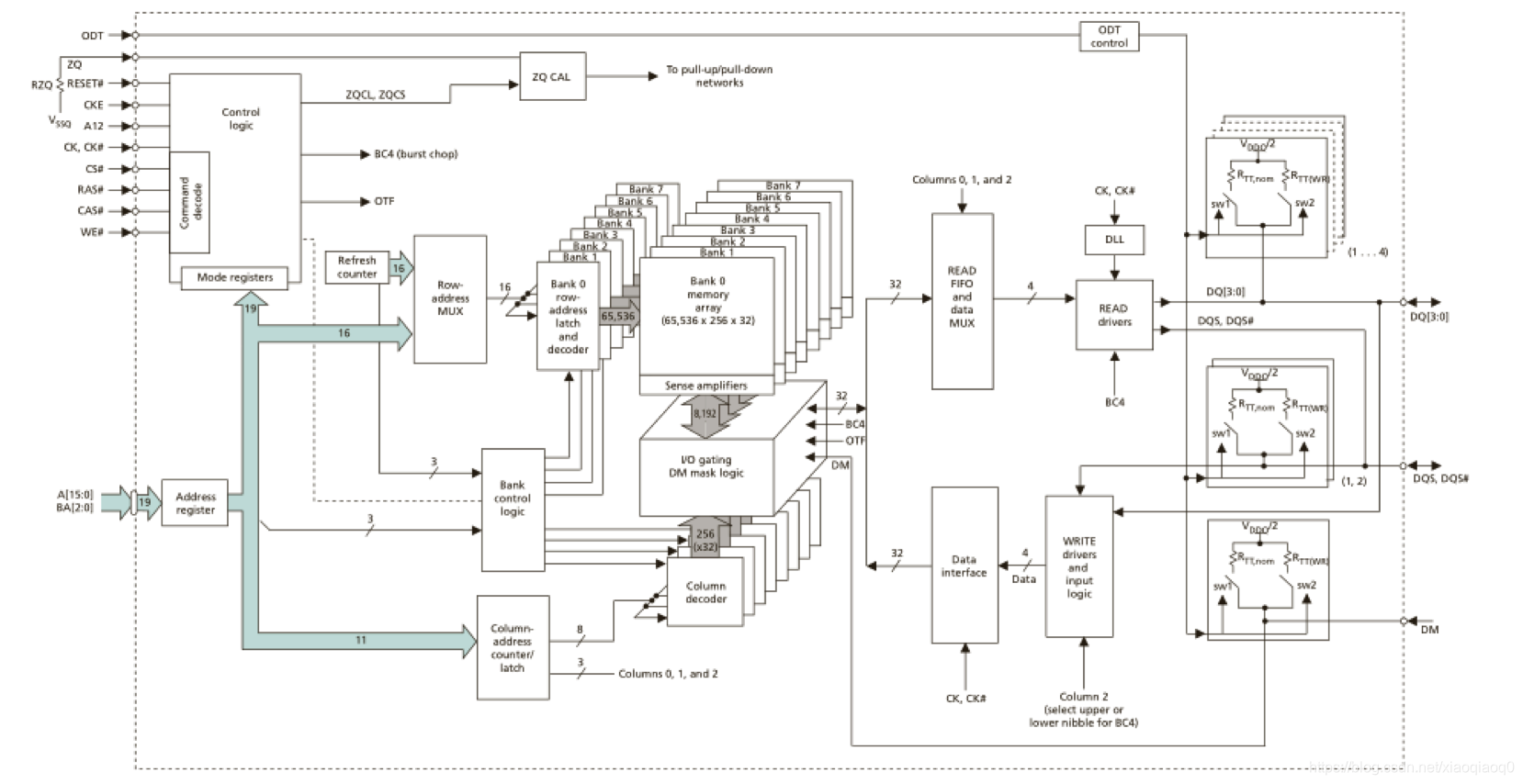

1.5 寻址过程

- 逻辑控制核心初始化,mode register配置;这个配置不做过多了解;

- 行有效RAS,确认如下信息:

- 片选CS

- bank地址

- 行地址A0~An

- 列有效CAS,确认如下信息:

- 地址线与行地址线复用A0~An

- 片选CS、bank地址仍在

- 读写命令通过WE信号确认;

则可确认我们所需要的地址;

两个例子:

- 一个DDR3L的组成结构:

- 一个LPDDR4的组成结构:

2. 总结

经过整理本部分内容,后续可以处理哪些问题?

- 某款SOC 和 某款DDR是否可以搭配:

- 规格是否支持?即支持协议版本?

- 是否支持多channel、多die?

- 频率是否支持?

- 某款SOC 和 某款DDR需要如何搭配:

- 确认SOC DQ线路和DDR的规格;

- 主要是4 * 8bit? 2 * 16bit? 如果支持多channel则可以减少一些连接;

实质主要是各种信号连接做在哪一层的问题;

- 某款SOC最大能够支持多少的mem,从地址线这里就已经限制死了;

update 于 2020.08.04

版权声明:本文为xiaoqiaoq0原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。