因为8088在更多的时候工作在最小模式下,所以我们以它的最小模式下为例来介绍它的一些主要引线以及功能

8088本身是一个40个引脚的一个双列直插式芯片,每一个引脚都有它独特的功能,甚至有时候一个引脚包含两种意义

最小模式下主要引脚信号

-

第一组信号

上图中的1

如果是指令的话在内存里

如果是数据的话有可能在内存里,也有可能在接口

所以是两个地址

-

第二组信号

8088或8086他们的地址总线的宽度都是20位的,宽度是什么?地址总线它是一组导线,这一组导线大家并排在一起,就构成了宽度,所以我们经常说总线有多少根线就用宽度来描述,也就是它一共有20位地址信号,能产生2^20个编码

对于下图

低8位的分时复用就是同样这8根线,我们两个共用,但不是同时用,同时用就乱套了不知道是什么性质了,一定是先有地址才有数据(做一次访问,先生成地址,接着发控制信号,接着发数据信号),所以在低8位地址信号线上,先传输的是8位地址,接着传输的是8位数据信号

对于8088/8086,对外通道只有8位,所以这里只用了低8位地址信号和8位数据信号分时复用

- 高四位也是分时复用和状态信号

- 只有中间的8位是自己独用的

对于下图

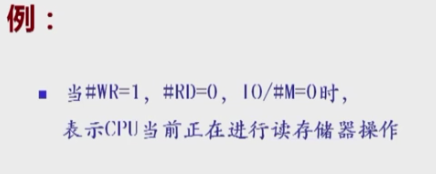

#号代表上横线,也就是低电平有效

DEN必须为低电平,数据收发器才能工作,才能进行读写

DTR为低电平的时候,数据是读入的,为高电平,就写

读和写的传输方向不一样,读是从外边把数据读进来,而写是把CPU的数据送出去,所以CPU在任意一个时间点上绝对不能既读又写

外部同步控制信号:CPU访问内存一次或者访问一次接口所需要的一个操作周期,正常情况下,是4个时钟周期,一个周期相当于0.2微妙,4个时钟周期称为一个总线周期,有时候4个时钟周期并不能完成,所以要增加一个时钟周期,所以Ready信号就是起这个作用的,CPU在访问内存或接口的时候,它会发出了一个这样的访问信号在第三个时钟周期它就开始检测各个引脚,如果它发现Ready端是高电平,就是Ready,就OK了,这个时候送上第四个周期,一次访问就结束了,如果Ready端是低电平,就必须在等待,它在第三个时钟周期的后边,插入一个时钟周期,插入的周期给它一个名字叫TW,等待周期,插入之后,再去检查Ready端,是低电平的话继续插…

-

第三组信号

-

第四组信号

版权声明:本文为qq_41386300原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。